Разработка контроллера на однокристальном микропроцессореРефераты >> Программирование и компьютеры >> Разработка контроллера на однокристальном микропроцессоре

1.2.2 Диаграммы состояний основных процессов

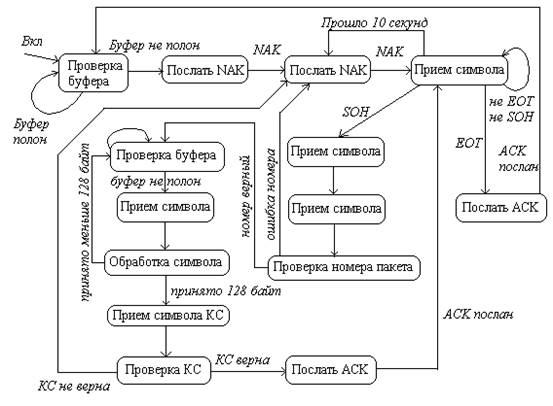

Диаграмма состояний процесса приема, показанная на рисунке 1.3, наглядно иллюстрирует работу контроллера при приеме данных от внешнего устройства.

Так как прием информации осуществляется пакетами, то в основе схемы лежит диаграмма состояний при использовании протокола X-Modem.

Рисунок 1.3 - Диаграмма состояний процесса приема данных

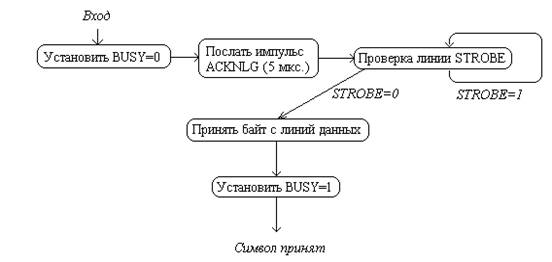

Более подробно состав блока «Послать символ» представлен на рисунке 1.4.

Рисунок 1.4 – Состав блока «Принять символ»

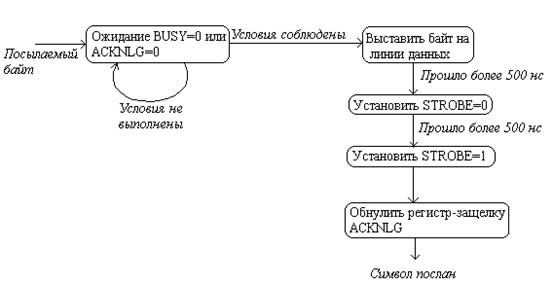

Содержание блока «Послать символ» раскрыто на рисунке 1.5.

Рисунок 1.5 – Состав блока «Послать символ».

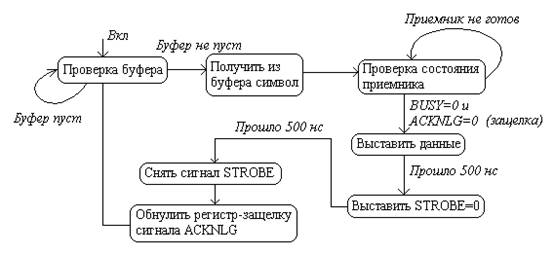

На рисунке 1.6 показана диаграмма процесса передачи информации. Передача ведется по одному байту без контроля ошибок.

На рисунке событие «Прошло 500 нс» означает выдержку необходимой паузы для формирования сигнала. Включение передатчика происходит при наличии флага готовности буфера передачи. Поэтому проверка буфера включает в себя и проверку состояния флага.

Рисунок 1.6 - Диаграмма состояний процесса передачи данных.

Диаграмма состояний процесса самодиагностики показана на рисунке 1.7.

Подсчет контрольной суммы ПЗУ (КС) ведется в цикле. В случае несовпадения рассчитанного значения с контрольными данными происходит останов процессора. Блок «Подсчет КС» обозначает циклический процесс по суммированию по модулю 256 содержимого ячеек ПЗУ.

Рисунок 1.7 - Диаграмма состояний процесса самодиагностики

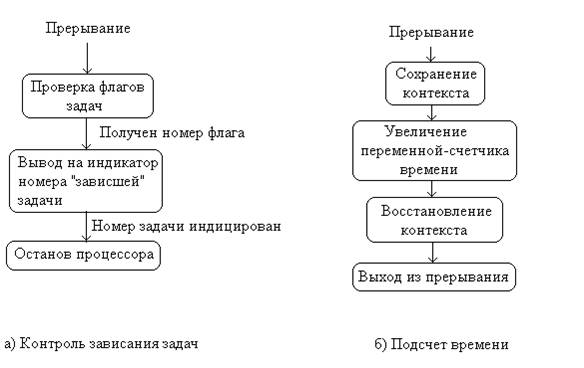

Диаграмма состояний процесса «службы времени» представлена на рисунке 1.8.

Служба времени решает две задачи. Это контроль зависания задач и формирование переменной, содержащей текущее время от начала работы контроллера. Конторль зависания осуществляется следующим образом. Перед началом каждого цикла прохода подпрограмм диспетчер запускает таймер, работающий в роли одновибратора. Время срабатывания таймера заведомо больше времени одного цикла работы диспетчера. Поэтому, если все задачи отработали успешно, таймер не успеет сработать до следующего перезапуска. Если таймер сработает и вызовет прерывание, то это сигнализирует о «зависании» одной из задач. В данной ситуации требуется немедленно остановить работу процессора. При подсчете времени таймер генерирует импульсы определенной частоты, по которым контроллер прерываний формирует запросы на прерывание для процессора. Обработчик этих прерываний каждый раз наращивает на единицу переменную-счетчик времени.

Рисунок 1.8 - Диаграмма состояний процесса «службы времени»

2 Разработка аппаратной части контроллера

2.1 Обоснование выбора микропроцессора

Шестнадцатиразрядный микропроцессор КР1810ВМ86 обеспечивает возможность эффективной работы с языками высокого уровня, имеет гибкую и мощную систему команд. Может быть использован как 16-ти так и 8-ми разрядный процессор. ВМ86 выполняет операции над битами, байтами, двухбайтовыми словами, действия знаковой и беззнаковой двоичной или десятичной арифметики, в том числе умножение и деление, имеет гибкую структуру аппаратурных и программных прерываний (до 256 типов).

К наиболее важным аппаратурным особенностям К1810ВМ86 относятся: развитая регистровая структура, существенно уменьшающая число обращений к памяти; конвейерный принцип выполнения команд с предварительной выборкой, обеспечивающий максимальную пропускную способность системной магистрали; распределенное микропрограммное устройство управления; мультиплексированная шина адреса-данных; многофункциональное использование выводов, позволяющее адаптировать МП к уровню сложности разрабатываемой системы; способность координировать взаимодействие нескольких процессоров.

2.2 Распределение адресного пространства

Микропроцессор К1810ВМ86 позволяет адресовать до 1Мбайт памяти. Так как основной задачей разрабатываемого контроллера является прием информации, преобразование в другой формат и передача ее следующему корреспонденту, то распределение память становится важной задачей. Особенности процессора заставляют выбирать такую структуру памяти, при которой младшие адреса занимает ОЗУ, а старшие – ПЗУ. Поставленная задача не требует реализации полного объема возможной памяти, поэтому используется следующая структура памяти:

- адреса 0000 – 3FFFh соответствуют ОЗУ;

- адреса 4000 – 7FFFh соответствуют ПЗУ.

Порты ввода-вывода, регистры управления таймера и программируемого контроллера прерывания также имеют фиксированные адреса:

- адреса 0000-0006 соответствуют порту ввода-вывода, предназначенному для приема данных;

- адреса 0008-000Еh соответствуют порту ввода-вывода, предназначенному для передачи данных;

- адреса 0010-0016h соответствуют управляющим регистрам программируемого таймера;

- адреса 0018-001Ah соответствуют управляющим регистрам программируемого контроллера прерываний.

2.3 Функциональная схема контроллера

Функциональная схема контроллера приведена в приложении.

Параллельный порт ввода-вывода PPI (DD15) предназначен для обеспечения приема информации в соответствии с протоколом X-Modem. Поэтому необходима двунаправленная связь. Фактически на микросхеме реализовано два интерфейса ИРПР-М. Один из них, для приема байтов информации, имеет следующую организацию:

- сигналы DIN 0 - DIN 7 – выводы РА0 – РА7;

- сигнал STROBEIN – вывод РС4;

- сигналы BUSYIN и ACKNLGIN – выводы РС0 и РС1 соответственно.

При приеме байта, он поступает на линии порта А (сигналы DIN 0 – DIN 7). Для передачи управляющих символов используется порт В. При этом служебные сигналы подключаются к следующим линиям:

- сигнал STROBEOUT – вывод РС2;

- сигналы BUSYOUT и ACKNLGOUT – выводы РС5 и РС6 соответственно.

Для передачи информации используется параллельный порт ввода-вывода PPI (DD16) На нем также реализован интерфейс ИРПР-М. Данные выдаются через порт А. Сигнал STROBE поступает в линию связи через нулевой разряд порта В. Сигналы готовности приемника BUSY и ACKNLG поступают в порт С (разряды 1 и 0 соответственно). Так как импульс ACKNLG имеет длительность около 5 мкс, то его программная фиксация в режиме параллельной обработки нескольких задач затруднена. Предусмотрена аппаратная защелка этого сигнала с помощью триггера. После получения сигнала ACKNLG триггер программно сбрасывается. Аналогичная схема присутствует и в блоке приема данных.

Индикатор готовности выполнен на дешифраторе DD28. Его адресные входы подсоединены к линиям 4, 5, 6 порта С микросхемы DD16. Регистр в нормальном рабочем режиме управляет индикатором готовности системы, а в случае конфликтной ситуации отображает номер «зависшей» задачи.

Программируемый таймер используется для отсчета интервалов времени для контроля выполнения задач и вызова прерываний для самопроверки контроллера – подсчета контрольной суммы ПЗУ. В качестве счетных импульсов к таймеру подведен сигнал с выхода PCLK системного генератора, имеющий частоту, в два раза меньшую, чем тактовая частота процессора. При частоте процессора 5 МГц таймер отсчитывает импульсы с частотой 2,5 МГц. При этом максимальная задержка, обеспечиваемая таймером равна 26 мс.