Классификация оперативной памятиРефераты >> Программирование и компьютеры >> Классификация оперативной памяти

П Л А Н

Память.

Классификация оперативной памяти (ОЗУ)

Введение

1. Энергозависимая и энергонезависимая память

2. SRAM и DRAM.

2.1. Триггеры.

2.2. Элементная база логики.

2.3. SRAM. Замечания.

2.4. DRAM. Что это такое?

3. Динамическое ОЗУ.

3.1. Устаревшие модификации.

3.1.1. DIP.

3.1.2. SIPP (SIP) —модули памяти.

3.2. SIMM-модули.

3.2.1. Сравнение SIMM-модулей.

3.2.2. Причины повышения скорости работы EDO RAM.

3.3.DIMM

3.3.1. SDRAM.

3.3.2. ESDRAM.

3.3.3. SDRAM II.

3.3.4. SLDRAM.

3.3.5. Память от Rambus (RDRAM, RIMM).

4. Оперативная кэш-память.

5. Постоянное запоминающее устройство.

6. Флэш-память.

7. CMOS-память.

8. Недостатки перезаписываемой памяти.

8.1. Потеря данных в CMOS.

8.2. Потеря данных в flash-памяти.

Память.

Одним из важнейших устройств компьютера является память, или запоминающее устройство (ОЗУ). По определению, данном в книге "Информатика в понятиях и терминах", ОЗУ - "функциональная часть цифровой вычислительной машины, предназначенной для записи, хранения и выдачи информации, представленных в цифровом виде." Однако под это определение попадает как собственно память, так и внешние запоминающие устройства (типа накопителей на жестких и гибких дисках, магнитной ленты, CD-ROM), которые лучше отнести к устройствам ввода/вывода информации. Таким образом под компьютерной памятью в дальнейшем будет пониматься только "внутренняя память компьютера: ОЗУ, ПЗУ, кэш память и флэш-память". Итак, рассмотрим классификацию внутренней памяти компьютера.

Классификация оперативной памяти (ОЗУ)

Введение

Оперативное запоминающее устройство является, пожалуй, одним из самых первых устройств вычислительной машины. Она присутствовала уже в первом поколении ЭВМ по архитектуре (“Информатика в понятиях и терминах”), созданных в сороковых — в начале пятидесятых годов двадцатого века. За эти пятьдесят лет сменилось не одно поколение элементной базы, на которых была построена память. Поэтому автор приводит некоторую классификацию ОЗУ по элементной базе и конструктивным особенностям.

1. Энергозависимая и энергонезависимая память

ЭВМ первого поколения по элементной базе были крайне ненадежными. Так, среднее врем работы до отказа для ЭВМ “ENIAC” составляла 30 минут. Скорость счета при этом была не сравнима со скоростью счета современных компьютеров. Поэтому требования к сохранению данных в памяти компьютера при отказе ЭВМ были строже, чем требования к быстродействию оперативной памяти. Вследствие этого в этих ЭВМ использовалась энергонезависимая память.

|

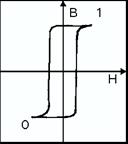

Рис. B.1. Диаграмма намагниченности ферритов.

|

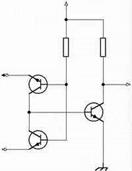

Рис. B.2. Схема элемента памяти на ферритовых сердечниках.

Полупроводниковая память.

В отличие от памяти на ферритовых сердечниках полупроводниковая память энергозависимая. Это значит, что

при выключении питания ее содержимое теряется.

Преимуществами же полупроводниковой памяти перед ее заменителями являются:

· малая рассеиваемая мощность;

· высокое быстродействие;

· компактность.

Эти преимущества намного перекрывают недостатки полупроводниковой памяти, что делают ее незаменимой в ОЗУ современных компьютеров.

2. SRAM и DRAM.

Полупроводниковая оперативная память в настоящее время делится на статическое ОЗУ (SRAM) и динамическое ОЗУ (DRAM). Прежде, чем объяснять разницу между ними, рассмотрим эволюцию полупроводниковой памяти за последние сорок лет.

2.1. Триггеры.

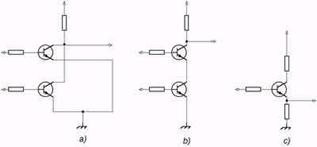

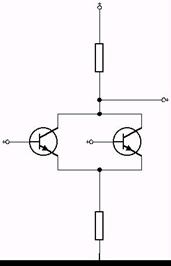

Триггером называют элемент на транзисторах, который может находиться в одном из двух устойчивых состояний (0 и 1), а по внешнему сигналу он способен менять состояние [Информатика в понятиях и терминах/М., Просвещение, 1991 г. — 208 с.: ил. — стр. 91]. Таким образом, триггер может служить ячейкой памяти, хранящей один бит информации. Любой триггер можно создать из трех основных логических элементов: И, ИЛИ, НЕ. Поэтому все, что относится к элементной базе логики, относится и к триггерам. Сама же память, основанная на триггерах, называется статической (SRAM).

2.2. Элементная база логики.

1.  РТЛ —резистивно-транзисторна логика. Исторически является первой элеентной базой логики, работающей на ЭВМ второго поколения. Обладает большой рассеивающей мощностью (свыше 100 мВт на логический элемент). Не применялась уже в ЭВМ третьего поколения.

РТЛ —резистивно-транзисторна логика. Исторически является первой элеентной базой логики, работающей на ЭВМ второго поколения. Обладает большой рассеивающей мощностью (свыше 100 мВт на логический элемент). Не применялась уже в ЭВМ третьего поколения.

2. ТТЛ, или Т2Л —транзисторно-транзисторна логика. Реализована на биполярных транзисторах. Использовалась в интегральных схемах малой и средней степени интеграции. Обладает временем задержки сигнала в логическом элементе 10— нс, а потребляемая мощность на элемент —10 мВт.

3.  ТТЛ-Шотки —это модификация ТТЛ с использованием диода Шотки. Обладает меньшим временем задержки (3 нс) и высокой рассеиваемой мощностью (20 мВт).

ТТЛ-Шотки —это модификация ТТЛ с использованием диода Шотки. Обладает меньшим временем задержки (3 нс) и высокой рассеиваемой мощностью (20 мВт).

4.

|