Программно-аппаратное обеспечениеРефераты >> Программирование и компьютеры >> Программно-аппаратное обеспечение

Основными разновидностями статической памяти (SRAM) с точки зрения организации ее функционирования являются асинхронная (Asynchronous), синхронная пакетная (Synchronous Burst) и синхронная конвейерно-пакетная (Pipeline Burst) память.

Динамические ЗУ с произвольным доступом

Как отмечалось выше, в качестве оперативных ЗУ в настоящее время чаще используются динамические ЗУ с произвольным доступом (DRAM). Такое положение обусловлено тем, что недостатки, связанные с необходимостью регенерации информации в таких ЗУ и относительно невысоким их быстродействием, с лихвой компенсируются другими показателями: малыми размерами элементов памяти и, следовательно, большим объемом микросхем этих ЗУ, а также низкой их стоимостью.

Широкое распространение ЗУ этого типа проявилось также и в разработке многих его разновидностей: асинхронной, синхронной, RAMBUS и других. Основные из них рассматриваются далее.

Асинхронная динамическая память DRAM

В процессе совершенствования технологии производства изменялась и логика функционирования динамических ОЗУ.

Первые такие ЗУ, которые впоследствии стали называть асинхронными динамическими ОЗУ, выполняли операции чтения и записи, получив лишь запускающий сигнал (обычно, сигнал строба адреса) независимо от каких-либо внешних синхронизирующих сигналов. Адрес элемента на шины адреса поступает двумя частями: адрес строки и адрес столбца.

Это PageModeDRAM– память со страничным режимом доступа. Диапазон адресов, находящихся в рамках одной строки, называется страницей.

На одно (полное) обращение уходило от 5 до 7 циклов системной шины в зависимости от ее частоты, особенностей используемого чипсета и, собственно, быстродействия памяти. Так, для системной шины с частотой 66 МГц длительность цикла составляет порядка 15 нс, что для 5 – 7 циклов дает диапазон 75 – 100 нс, если же частота системной шины составляла 100 Мгц, то 5 циклов занимают 50 нс.

Подача адреса двумя частями удлиняет цикл обращения к памяти. Вместе с тем, большинство обращений непосредственно к оперативной памяти производится по последовательным адресам.

Поскольку адрес строки является старшей частью адреса, то для последовательных адресов памяти адрес строки одинаков (исключение составляет переход через границу строки). Это позволяет в (пакетном) цикле обращений по таким адресам задать адрес строки только для обращения по первому адресу, а для всех последующих задавать только адрес столбца. Такой способ получил название FPM (Fast Page Mode – быстрый страничный режим) и мог реализовываться обычными микросхемами памяти при поддержке контроллера памяти чипсета, обеспечивая сокращение времени обращения к памяти для всех циклов пакета, кроме первого.

Следующей модификацией асинхронной динамической памяти стала память EDO (Extended Data Output – растянутый выход данных). В этих микросхемах за счет введения двухступенчатого конвейера при выходе не обязательно ждать чтения всей строки. Получается ускорение доступа только при чтении.

Впоследствии появилась и еще одна (последняя) модификация асинхронной DRAM – BEDO (Burst EDO – пакетная EDO память), в которой не только адрес строки, но и адрес столбца подавался лишь в первом цикле пакета, а в последующих циклах адреса столбцов формировались с помощью внутреннего счетчика. Это позволило еще повысить производительность памяти.

Синхронная динамическая память SDRAM

Синхронная динамическая память обеспечивает большее быстродействие, чем асинхронная, при использовании аналогичных элементов памяти.

Выигрыш в производительности SDRAM достигается за счет более гибкого управления процессами чтения и записи, возможности задания параметров и лучших алгоритмов работы контроллера памяти.

Во-первых, в SDRAM памяти процессы синхронны, что позволяет более жестко упорядочить их во времени.

Во-вторых, микросхемы SDRAM имеют внутреннюю мультибанковую организацию. Это позволяет применять приемы, повышающие пропускную способность памяти. В частности, можно прибегнуть к чередованию, или расслоению, (interleave) адресов. Кроме того, оказывается возможным в ряде случаев так спланировать порядок обработки обращений к памяти, чтобы уменьшить их времена. Однако, это не совсем простая задача, так как необходимо учитывать временные ограничения на различные сочетания следующих друг за другом операций, длину пакетных циклов, особенности выполнения подзаряда. Поэтому чипсеты различных производителей обеспечивают разную пропускную способность памяти. Лучше всего решение этой задачи для ПЭВМ удается фирме Intel.

Действительно, в общем случае процедура записи или чтения в SDRAM памяти выполняется в три этапа:

1. Сначала при подаче сигнала происходит выбор нужной строки, или, в терминах, принятых для этой памяти, выполняется команда активации банка.

2. Затем, выполняются требуемые операции записи или чтения и передачи данных.

3. После записи или чтения строку, к которой выполнялось обращение, надо закрыть (выполнить подзаряд банка), иначе нельзя будет обратиться к новой строке этого же банка (вновь его активировать).

Именно за счет первого и последнего этапов и можно добиться ускорения работы памяти. Если очередное обращение к данному банку будет адресоваться к той же строке, то ее можно не закрывать, что позволит не выполнять заново команду активации банка.

DDR SDRAM

Следующим шагом в развитии SDRAM стала память DDR SDRAM, обеспечивающая двойную скорость передачи данных (DDR – Double или Dual Data Rate), в которой за один такт осуществляются две передачи данных – по переднему и заднему фронтам каждого синхроимпульса. Во всем остальном эта память работает аналогично обычной SDRAM памяти (которую стали иногда называть SDR SDRAM – Single Data Rate). Времена задержек CAS Latency для DDR SDRAM могут быть 2 и 2,5 такта.

Однако производительность DDR SDRAM вовсе не в 2 раза выше, чем производительность обычной SDRAM, так как ускорение касается только собственно передачи данных, основные задержки остались теми же.

Коммерческие названия SDR и DDR типов памяти SDRAM несколько различаются. Для обычной памяти используют для указания скоростных характеристик рабочую частоту системной шины: PC100, PC133, что соответствует времени такта синхроимпульсов 10 нс и 7,5 нс. Тогда как для DDR SDRAM указывают скорость передачи данных, что с учетом передачи за один раз 8 байтов данных дает скорости (при двух передачах за такт) при частоте шины 133 МГц – 2 × 133 × 8 = 2128 Мбайт/с, при частоте 166 МГц – 2 × 166 × 8 = 2656 и при частоте 200 МГц – 2 × 200 × 8 = 3200. Такую память маркируют PC2100, PC2700 и PC3200, соответственно, причем этот ряд постоянно растет. Дальнейшим развитием SDRAM является стандарт DDR2

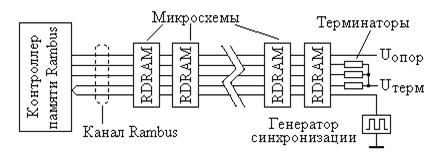

Динамическая память RDRAM

Память RDRAM (Rambus DRAM) построена на таких же элементах памяти, как и рассмотренные выше виды динамической памяти. Она относится к тому направлению разработок, в котором производительность памяти (ее пропускная способность, вычисляемая как произведение разрядности шины данных и частоты передачи по ней) достигается за счет увеличения частоты, при уменьшении разрядности шины данных. Последнее обстоятельство способствует снижению взаимных помех от проводников шины, особенно сказывающихся на высоких частотах.

|