Блок памятиРефераты >> Радиоэлектроника >> Блок памяти

Для уменьшения емкостной нагрузки системной шины внутренние шины адреса и данных блоков подключаем к ней через буферные формирователи построенные на микросхемах К1554АП6. Причем разобьём БП на две составные части: блок ПЗУ и блок ОЗУ. Входы и выходы этих блоков подключим к разным буферным формирователям.

Составим карту памяти заданного устройства:

|

А14 |

А13 |

А12 |

А11 |

А10 |

А9 |

А8 |

А7 |

А6 |

А5 |

А4 |

А3 |

А2 |

А1 |

А0 |

Узел |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ПЗУ |

|

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

ПЗУ |

|

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

ПЗУ |

|

1 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

ОЗУ |

|

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

Х |

ОЗУ |

|

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

ОЗУ |

Для адресации разрабатываемого БП можно использовать четыре дешифратора 1554ИД7 (имеющим организацию 3*8). Старшие разряды адресов используются для подачи сигналов на входы разрешения дешифраторов.

3.2. Разработка селектора адреса.

Так как выбор между блоками ПЗУ и ОЗУ осуществляется разрядами адреса (А12¸А14), будем использовать эти адреса для синтезирования схемы селектора адреса.

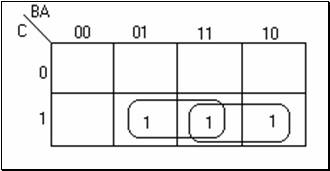

Синтезируем схему селектора адреса с помощью карт Карно.

|

| А14 C | А13 B | А12 A | F |

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 |