Блок памятиРефераты >> Радиоэлектроника >> Блок памяти

![]()

![]()

![]()

![]()

![]() F=CA+CB=CA+CB=CA × CB

F=CA+CB=CA+CB=CA × CB

Для управления работой селектора адреса используем сигналы ![]() и

и ![]() , так как определенный блок выбирается низким уровнем сигнала.

, так как определенный блок выбирается низким уровнем сигнала.

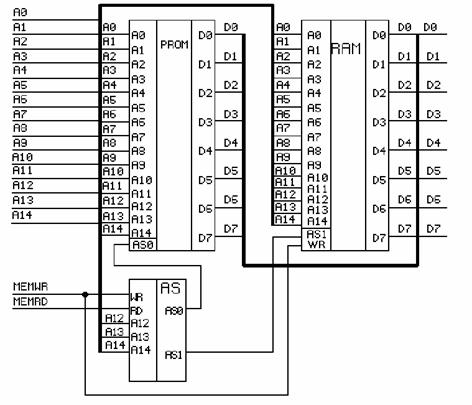

Селектор адреса вырабатывает сигналы AS0 и AS1, при обращении к ПЗУ и ОЗУ, соответственно. При этом оба этих сигнала активно низкие. Сигналы AS0 или AS1 только тогда будут выбирать один из блоков памяти, когда один из сигналов MEMWR или MEMRD будет активным низким. Если же оба сигнала будут активно высокими, то это будет запретом обращения к памяти.

3.3. Временная диаграмма работы БП.

|

![]() A

A

|

![]()

|

RD

|

| ||||

tA – время установки адреса

tp1 – время считывания (40 нс для 556РТ20);

tH1 – время удержания адреса

4. Расчет электрических параметров блока памяти.

Максимально допустимое количество объединяемых входов КI микросхем памяти определим из того, что суммарные токи нагрузки для высокого и низкого уровней сигнала и емкостная нагрузка не должны превышать значений, допустимых для выхода буферного каскада, используемого в данной цепи:

![]() ,

,

где IOH , IOL, COL - максимально допустимые значения токов нагрузки высокого и низкого уровней и емкости нагрузки буферного элемента, IIH, IIL, CI - входные токи высокого и низкого уровней и емкость входов, СМ - емкость монтажа.

KIПЗУ=min(76*10-3/0.25*10-3;81*10-3/40*10-6;500-20/15)=32

KОЗУ=min(76*10-3/0.2*10-3;81*10-3/4*10-6;500-20/10)=48

Так как у нас используется 20 микросхем, то условие выполняется.

Определяем максимально допустимое количество объединяемых выходов КО

![]() ,

,

где CLMAX - максимально допустимая емкость нагрузки выхода, CO - емкость выхода, C I , NIN - емкость и количество входов, подключенных к данному выходу, CM - емкость монтажа.

200СLMAXПЗУ>=8(20-1)+15*1+20=187

200СLMAXОЗУ>=7(20-1)+15*1+20=168

Из расчета видно что для буферизации ШД достаточно одной МС буфера К1554АП6 как для ПЗУ так и для ОЗУ.

При расчете динамических параметров разработанного блока памяти учтём тот факт, что времена задержек распространения сигнала, указаны для емкости нагрузки CL = 50 пФ. Скорректируем значения времен задержек распространения сигналов в большую сторону из расчета: - 0.07 нс/пФ.

tОЗУ=16+10+(60+118*0,07)+13=107,26 нс (в режиме записи)

tОЗУ=16+10+(60+118*0,07)+13=107,26 нс (в режиме считывания)

tПЗУ=16+10+(40+137*0,07)+13=112,39 нс

Мощность, потребляемая блоком памяти, (PCC) определяется как сумма средних мощностей, потребляемых микросхемами памяти и логики, на которых реализованы схемы управления.

PЛОГ =2PАП6+4PИД7+PЛП5+PЛН1

PЛОГ =2*80*10-6*5+4*80*10-6*5+40*10-6*5+40*10-6*5=2,8мВт

Для режима хранения получим:

PCCXP=PXPПЗУ*NПЗУ+ PXPОЗУ*NОЗУ+ PЛОГ

PCCXP=900*20+250*20+2,8=23Вт

При расчете мощности, потребляемой микросхемами памяти в режиме обращения, учтём тот факт, что в активном режиме находятся БИС только одного выбранного столбца матрицы памяти, а все остальные БИС памяти переведены в энергосберегающий режим. «Наихудший» случай когда обращение происходит к блоку ОЗУ. Тогда для этого режима работы блока памяти имеем :

PCCO=PXPПЗУ *NОЗУХР + PXРОЗУ NОЗУХР + PОЗУОБР *NОЗУОБР+PЛОГ

PCCO =20*900+18*250+2*900+2.8=23.4Вт

ГРАФИЧЕСКАЯ ЧАСТЬ.

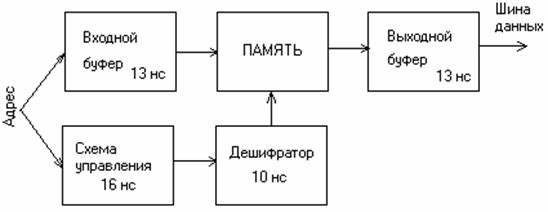

1. Функциональная схема блока памяти.

|

Литература

1. Ермаков А. Е., Ермакова О.П. Задание на курсовую работу с методическими указаниями по дисциплине «Схемотехника» /РГОТУПС. -М.: 1999. -10 с.

2. Ермаков А. Е., Схемотехника ЭВМ. Учебное пособие. -М.: РГОТУПС, 1997. -352 с.