Системы диагностики ПКРефераты >> Программирование и компьютеры >> Системы диагностики ПК

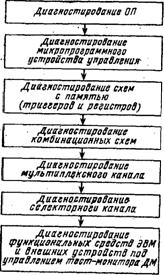

Рис. 9 Операции, выполняемые при диагностировании по методу двухэтапного диагностирования

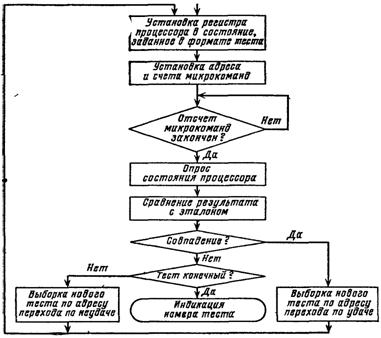

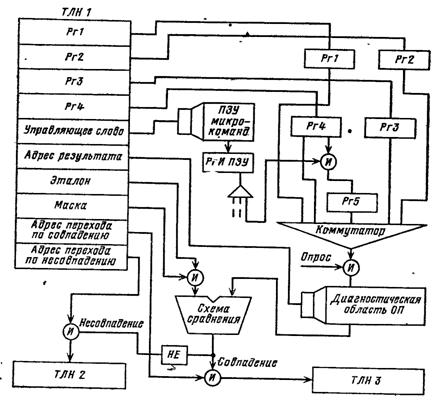

В тестах, предназначенных для проверки комбинационных схем, управляющая информация задает адрес микрооперации приема сигнала с выхода комбинационной схемы в выходной регистр (рис. 10).

Рис.10. Схема выполнения одного ТЛН

Управляющая информация может задавать адреса микроопераций, обеспечивающих передачу тестового воздействия на вход проверяемых средств и транспортировку результата в триггеры, имеющие опрос.

С помощью операции «Опрос» записывается состояние всех регистров и триггеров ДУ в оперативную или служебную память.

Для выполнения операции «Опрос» в аппаратуру ДУ вводятся дополнительные связи с выходов регистров и триггеров на вход блока коммутации СТД, связанного с информационным входом оперативной или служебной памяти.

С помощью операции «Сравнение я ветвление» обеспечивается сравнение ответа ДУ на тестовое воздействие с эталонной информацией. ТЛН задается адрес состояния проверяемого регистра или триггера в оперативной и служебной памяти, записываемого с помощью операции «Опрос», а также его эталонное состояние. Возможны два исхода операции «Сравнение и ветвление»— совпадение и несовпадение ответа с эталоном. Метод двухэтапного диагностирования использует, как правило, условный алгоритм диагностирования. Поэтому ТЛН содержит два адреса ветвления, задающих начальный адрес следующих ТЛН в оперативной памяти.

Для хранения ТЛН, как правило, используется магнитная лента, а для их ввода — стандартные или специальные каналы ввода.

Тесты локализации неисправностей обычно загружаются в оперативную память и подзагружаются в нее по окончании выполнения очередной группы ТЛН. Поэтому до начала диагностики по методу ТЛН проверяется оперативная память и микропрограммное управление.

При обнаружении отказа на пульте индицируется номер теста, по которому в диагностическом справочнике отыскивается неисправный сменный блок.

В качестве примера реализации метода двухэтапного диагностирования рассмотрим систему диагностирования процессора ЭВМ ЕС-1030. Для нормальной загрузки и выполнения диагностических тестов процессора ЭВМ ЕС-1030 необходима исправность одного из селекторных каналов и начальной области оперативной памяти (ОП). Поэтому вначале выполняется диагностирование ОП. Для этого имеется специальный блок, обеспечивающий проверку ОП в режимах записи и чтения нулей (единиц) тяжелого кода/обратного тяжелого кода. Неисправность ОП локализуется с точностью до адреса и бита.

Следующие стадии диагностирования, последовательность которых приведена на рис. 11, используют уже проверенную оперативную память.

На нервов стадии диагностические тесты загружаются в начальную область ОП (первые 4 Кслов) и затем выполняются с помощью диагностического оборудования. Тесты расположены на магнитной ленте в виде массивов. После выполнения тестов очередного массива в ОП загружается и выполняется следующий массив тестов. Загрузка тестов выполняется по одному из селекторных каналов в специальном режиме загрузки ТЛН.

|

|

|

На второй стадии диагностирования проверяется микропрограммная память процессора, которая используется на следующих стадиях диагностирования. В ней содержатся микропрограммы операций установки, опроса, сравнения и ветвления.

На третьей стадии диагностирования выполняется проверка триггеров (регистров) процессора. Эти тесты называются тестами нулевого цикла. Опрос состояния триггеров (регистров) выполняется по дополнительным линиям опроса. Триггеры (регистры) проверяются на установку в 0-1-0. Результаты проверки сравниваются с эталонными, записанными в формате теста. Место неисправности определяется по номеру теста, который обнаружив несоответствие. В диагностическом справочнике тестов нулевого цикла номеру теста соответствует конструктивный адрес и название неисправного триггера на функциональной схеме.

С помощью тестов единичного цикла проверяются комбинационные схемы. Их последовательность определяется условным алгоритмом диагностирования. Тесты комбинационных схем выполняются следующим образом: с помощью операции установки в регистре процессора, расположенном на входе проверяемой комбинационной схемы, задается состояние, соответствующее входному тестовому воздействию. Выполняется микрооперация приема выходного сигнала комбинационной схемы в регистр расположенный на выходе комбинационной; схемы; Состояние этого регистра записывается в диагностическую область ОП, а затем сравнивается с эталонным. В зависимости от исхода теста выполняется переход к следующему тесту При обнаружении неисправности индицируется .номер теста. В диагностическом справочнике тестов единичного цикла указаны не только подозреваемые ТЭЗ, но и значения сигналов на входах, промежуточных точках и выходах комбинационной схемы. Такая подробная информация дозволяет уточнить локализацию до монтажных связей или микросхем. На следующих стадиях диагностирования, использующих другие методы диагностирования, проверяются мультиплексный и селекторный каналы, а также функциональные средства ЭВМ с помощью тест-секций диагностического монитора.

3. МЕТОД ПОСЛЕДОВАТЕЛЬНОГО СКАНИРОВАНИЯ.

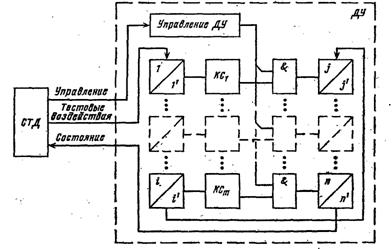

Метод последовательного сканирования является вариантом метода двухэтапного диагностирования, при котором схемы с памятью (регистры и триггеры) в режиме диагностирования превращаются в один сдвигающий регистр с возможностью установки его в произвольное состояние и опроса с помощью простой операции сдвига.

Обобщенная схема системы диагностирования, использующей метод последовательного сканирования, показана на рис. 12,

Рис. 12. Обобщенная схема системы диагностирования, реализующей метод последовательного сканирования:

1, .,i, l, . n — основная часть регистра; 1', .i', l', ., n'—дополнительная часть регистра (триггеры образования сдвигового регистра)

Этот метод получил распространение в ЭВМ на больших интегральных микросхемах (БИС). Вместе с очевидными достоинствами БИС их использование затрудняет проблему диагностирования ЭВМ в связи с ограниченными возможностями доступа к схемам, расположенным внутри БИС. При диагностировании ЭВМ, построенной на БИС,