ОперативкаРефераты >> Программирование и компьютеры >> Оперативка

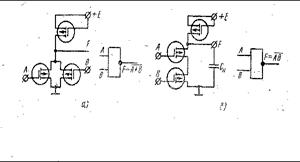

4. ИИЛ, или И2Л —интегральная инжекторная логика. Это разновидность ТТЛ, базовым элементом которой являются не биполярные транзисторы одного рода (pnp или npn), а горизонтально расположенного pnp транзистора и вертикально расположенного npn транзистора. Это позволяет создать высокую плотность элементов на БИС и СБИС. При этом потребляемая мощность равна 50 мкВт на элемент и время задержки сигнала – 10 нс.

5.

|

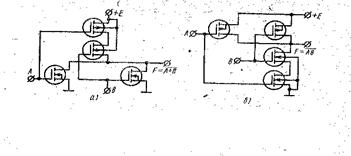

6. Элементы на МДП (МОП) —транзисторах. Это схемы, в которых биполярные транзисторы заменены на полевые. Время задержки таких элементов составляет от 1 до 10 нс, потребляемая мощность — от 0,1 до 1,0 мВт

7. КМОП —логика (комплементарная логика.) В этой логике используются симметрично включенные n-МОП и p-МОП транзисторы. Потребляема мощность в статическом режиме —50 мкВт, задержка —10 —50 нс.

Как видно из этого обзора, логика на биполярных транзисторах самая быстрая, но одновременно самая дорогая и обладает высокой мощностью рассеяния . При прочих равных условиях логика на полевых транзисторах более медленная, но обладает меньшим электропотреблением и меньшей стоимостью.

1.2 Быстродействие и производительность памяти

Быстродействие памяти определяется временем выполнения операций записи и считывания данных. Основными параметрами любых элементов памяти является минимальное время доступа и длительность цикла обращения. Время доступа (access time) определяется как задержка появления действительных данных на выходе памяти относительно начала цикла чтения. Длительность цикла определяется как минимальный период следующих друг за другом обращений к памяти, причем циклы чтения и записи могут требовать различных затрат времени. В цикл обращения кроме активной фазы самого доступа входит и фаза восстановления (возврата памяти к исходному состоянию), которая соизмерима по времени с активной фазой. Временные характеристики самих запоминающих элементов определяются их принципом действия и используемой технологией изготовления.

Производительность памяти можно характеризовать как скорость потока записываемых или считываемых данных и измерять в мегабайтах в секунду. Производительность подсистемы памяти наравне с производительностью процессора существенным образом определяет производительность компьютера. Выполняя определенный фрагмент программы, процессору придется, во-первых, загрузить из памяти соответствующий программный код, а во-вторых, произвести требуемые обмены данными, и чем меньше времени потребуется подсистеме памяти на обеспечение этих операций, тем лучше.

Производительность памяти, как основной, так и кэша второго уровня, обычно характеризуют длительностью пакетных циклов чтения (Memory Burst Read Cycle). Пакетный режим обращения является основным для процессоров, использующих кэш (486 и выше); циклы чтения выполняются гораздо чаще, чем циклы записи (хотя бы потому, что процессору приходится все время считывать инструкции из памяти). Эта длительность выражается в числе тактов системной шины, требуемых для передачи очередной порции данных в пакете. Обозначение вида 5-3-3-3 для диаграммы пакетного цикла чтения соответствует пяти тактам на считывание первого элемента в цикле и трем тактам на считывание каждого из трех последующих элементов. Первое число характеризует латентность (latency) памяти — время ожидания данных, последующие — скорость передачи. При этом, конечно же, оговаривается и частота системной шины. По нынешним меркам хорошим результатом является цикл 5-1-1-1 для частоты шины 100 или 133 МГц. Однако для процессоров Pentium 4, у которых за каждый такт синхронизации системной шины передается по четыре 64-битных слова данных, возможно, будет иной способ выражения производительности памяти.

Производительность подсистемы памяти зависит от типа и быстродействия применяемых запоминающих элементов, разрядности шины памяти и некоторых «хитростей» архитектуры.

Разрядность шины памяти — это количество байт (или бит), с которыми операция чтения или записи может быть выполнена одновременно. Разрядность основной памяти обычно согласуется с разрядностью внешней шины процессора (1 байт - для 8088; 2 байта - для 8086, 80286, 3865Х; 4 байта - для 386DХ, 486; 8 байт — для Pentium и выше). Вполне очевидно, что при одинаковом быстродействии микросхем или модулей памяти производительность блока с большей разрядностью будет выше, чем у малоразрядного. Именно с целью повышения производительности у 32-битных (по внутренним регистрам) процессоров Реntium и выше внешняя шина, связывающая процессор с памятью, имеет разрядность 64 бита. Желание производителей процессоров и системных плат сэкономить на разрядности памяти всегда приводит к снижению производительности: компьютеры на процессорах с полноразрядной шиной (8086, 386DХ) более чем на 50 % обгоняют своих «младших братьев» (8088, 3865Х) при одинаковой тактовой частоте. Одно время выпускались чипсеты, работающие с 32-битной памятью даже для Pentium, но эффективность подобной экономии сомнительна.

Банком памяти называют комплект микросхем или модулей (а также их посадочных мест — «кроваток» для микросхем, слотов для SIММ или DIMM), обеспечивающий требуемую для данной системы разрядность хранимых данных. Работоспособным может быть только полностью заполненный банк. Внутри одного банка практически всегда должны применяться одинаковые (по типу и объему) элементы памяти.

В компьютерах на 486-х процессорах банком является один SIMM-72 или четверка SIMM-30. В компьютерах на процессорах 5-6 (а для АМD и 7-го) поколений банком может быть пара SIMM-72 или один модуль DIMM или RIММ (эти модули могут содержать и несколько банков). На платы с чипсетом i850 для процессора Pentium 4 требуется установка пар RIMM (чтобы обеспечить производительность памяти, достойную новой микроархитектуры).

Если устанавливаемый объем памяти набирается несколькими банками, появляется резерв повышения производительности за счет чередования банков (bank interleaving). Идея чередования заключается в том, что смежные блоки данных (разрядность такого блока данных соответствует разрядности банка) располагаются поочередно в разных банках. Тогда при весьма вероятном последовательном обращении к данным банки будут работать поочередно, причем активная фаза обращения к одному банку может выполняться во время фазы восстановления другого банка, то есть применительно к обоим банкам не будет простоя во время фазы восстановления. Частота передачи данных в системе с чередованием двух банков может быть удвоенной по отношению к максимальной частоте paботы отдельного банка. Для реализации чередования чипсет должен обеспечивать возможность перекоммутации адресных линий памяти в зависимости от установленного количества банков и иметь для них (банков) раздельные линии управляющих сигналов. Чем больше банков участвуют в чередовании, тем выше (теоретически) предельная производительность. Чаще всего используется чередование двух или трех банков (two way interleaving, three way interleaving). В чередовании может участвовать и большее число банков. Из разбиения на мелкие банки можно извлечь и другую выгоду. Поскольку современные процессоры; способны параллельно выставлять несколько запросов на транзакции с памятью, скрытые фазы обработки запросов, обусловленные необходимым временем доступа, относящихся к разным банкам, могут выполняться одновременно.