ОперативкаРефераты >> Программирование и компьютеры >> Оперативка

Недостатком можно посчитать придуманные производителем режимы управления питанием модулей. Если напряжение питания 2,5 В стало практически стандартом для всех новых технологий памяти DRAM, то режимы работы Асtive (активный), Standby (ожидания), NAP ("спящий") и PowerDown (отключение питания) - собственное изобретение Rambus. Самое интересное, что микросхема, не обменивающаяся в текущий момент данными с контроллером, автоматически переводится в режим ожидания, иначе возможен перегрев системы, так как тактовые частоты весьма высоки. На переключение же из режима Standby в активное состояние требуется 100 нс.

Хочется отметить, что реальная пропускная способность RDRAM существенно ниже заявленных Rambus значений. После появления системного набора Intel 820 с поддержкой DR DRAM были проведены сравнительные тесты с другими типами памяти. Оказалось, что на большинстве реальных задач RDRAM уступает даже SDRАМ, работающим на частоте 133 МГц. В значительной мере это объясняют более узкой шиной данных канала Rambus (16 бит) по сравнению с 64-битной шиной SDРАМ. С появлением чипсета VIА Ароllo Рго2бб, поддерживающего DDR DRАМ, картина для Rambus и Intel становится вовсе безрадостной.

2.2 Память типа SRAM

Существует тип памяти, совершенно отличный от других - статическая оперативная память (Static RAM – SRAM). Она названа так потому, что, в отличии от динамической оперативной памяти, для сохранения ее содержимого не требуется периодической регенерации. Но это не единственное ее преимущество. SRAM имеет более высокое быстродействие, чем динамическая оперативная память, и может работать на той же частоте, что и современные процессоры.

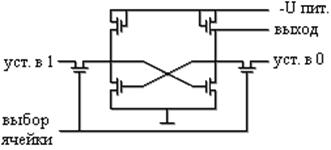

Время доступа SRAM не более 2 нс, это означает, что такая память может работать синхронно с процессорами на частоте 500 МГц или выше. Однако для хранения каждого бита в конструкции SRAM используется кластер из 6 транзисторов. Использование транзисторов, без каких либо конденсаторов означает, что нет необходимости в регенерации. Пока подается питание, SRAM будет помнить то, что сохранено.

Рис.2.2.1 Ячейка SRAM

Микросхемы SRAM не используются для всей системной памяти потому, что по сравнению с динамической оперативной памятью быстродействие SRAM намного выше, но плотность ее намного ниже, а цена довольно высокая. Более низкая плотность означает, что микросхемы SRAM имеют большие габариты, хотя их информационная емкость намного меньше. Большое число транзисторов и кластиризованное их размещение не только увеличивает габариты SRAM, но и значительно повышает стоимость технологического процесса по сравнению с аналогичными параметрами для микросхем DRAM.

Несмотря на это, разработчики все-таки применяют память типа SRAM для повышения эффективности РС. Но во избежание значительного увеличения стоимости устанавливается только небольшой объем высокоскоростной памяти SRAM, которая используется в качестве кэш-памяти. Кэш-память работает на тактовых частотах, близких или даже равных тактовым частотам процессора, причем обычно именно эта память используется процессором при чтении и записи.

В переводе слово «cache» (кэш) означает «тайный склад», «тайник» («заначка»). Тайна этого склада заключается в его «прозрачности» — адресуемой области памяти для программы он не добавляет. Кэш является дополнительным быстродействующим хранилищем копий блоков информации из основной памяти, вероятность обращения к которым в ближайшее время велика. Кэш не может хранить копию всей основной памяти, поскольку его объем во много раз меньше объема основной памяти. Он хранит лишь ограниченное количество блоков данных и каталог (cache directory) — список их текущего соответствия областям основной памяти. Кроме того, кэшироваться может и не вся оперативная память, доступная процессору: во-первых, из-за технических ограничений может быть ограничен максимальный объем кэшируемой памяти; во-вторых, некоторые области памяти могут быть объявлены некэшируемыми (настройкой регистров чипсета или процессора). Если установлено оперативной памяти больше, чем возможно кэшировать, обращение к некэшируемой области ОЗУ будет медленным. Таким образом, увеличение объема ОЗУ, теоретически всегда благотворно влияющее на производительность, может снизить скорость работы определенных компонентов, попавших в некэшируемую память. В ОС Windows память распределяется, начиная с верхних адресов физической памяти, в результате чего в некэшируемую область может попасть ядро ОС.

При каждом обращении к памяти контроллер кэш-памяти по каталогу проверяет, есть ли действительная копия затребованных данных в кэше. Если она там есть, то это случай кэш-попадания (cache hit) и данные берутся из кэшпамяти. Если действительной копии там нет, это случай кэш-промаха (cache miss), и данные берутся из основной памяти. В соответствии с алгоритмом кэширования блок данных, считанный из основной памяти, при определенных условиях заместит один из блоков кэша. От интеллектуальности алгоритма замещения зависит процент попаданий и, следовательно, эффективность кэширования. Поиск блока в списке должен производиться достаточно быстро, чтобы «задумчивостью» в принятии решения не свести на нет выигрыш от применения быстродействующей памяти. Обращение к основной памяти может начинаться одновременно с поиском в каталоге, а в случае попадания — прерываться (архитектура Look aside). Это экономит время, но лишние обращения к основной памяти ведут к увеличению энергопотребления. Другой вариант: обращение к основной памяти начинается только после фиксации промаха (архитектура Look Through), при этом теряется, по крайней мере, один такт процессора, зато экономится энергия.

Кэш в современных компьютерах строится по двухуровневой, а иногда и трехуровневой схеме.

Первичный кэш, или L1 Cache (Level 1 Cache), — кэш 1 уровня, внутренний (Internal, Integrated) кэш процессоров класса 486 и выше, а также некоторых моделей 386.

Вторичный кэш, или L2 Cache (Level 2 Cache), — кэш 2 уровня. Для процессоров вплоть до Pentium (и аналогичных) это внешний (External) кэш, установленный на системной плате. В Р6 и более мощных процессорах вторичный кэш расположен в одном корпусе с процессором, и для таких процессоров дополнительный кэш на системную плату уже не устанавливается.

Кэшем третьего уровня оказывается кэш, установленный на системной плате с сокетом 7, когда в него устанавливают процессор AMD K6-3, обладающий встроенным двухуровневым кэшем.

Объем первичного кэша невелик (8-128 Кбайт); чтобы повысить его эффективность, для данных и команд часто используется раздельный кэш (так называемая Гарвардская архитектура — противоположность Принстонской с общей памятью для команд и данных). В процессорах Pentium 4 первичный кэш устроен уже иначе.

Кэш-контроллер должен обеспечивать когерентность (coherency) — согласованность данных кэш-памяти обоих уровней с данными в основной памяти при том условии, что обращение к этим данным может производиться не только процессором, но и другими активными (bus-master) адаптерами, подключенными к шинам (PCI, VLB, ISA и т. д.). Следует также учесть, что процессоров может быть несколько, и у каждого может быть свой внутренний кэш.