ОперативкаРефераты >> Программирование и компьютеры >> Оперативка

2.1.7 SGRAM

Это аббревиатура для Синхронной графической памяти со случайным доступом (Synchronous Graphic Random Access Memory), типа DRAM, всё в большей степени используемом в видеоадаптерах и графических акселераторах. Как и SDRAM, SGRAM способна самосинхронизироваться с частотой шины процессора вплоть до частот около 100 МГц. Вдобавок к этому, SGRAM использует некоторые другие технологии, такие как шаблонная и блочная запись, для увеличения пропускной способности для интенсивно работающих с графикой приложений

2.1.8 DDRSDRAM (SDRAMII)

DDR SDRAM (Double Data Rate Synchronous Dynamic Random Access Memory) – динамическая синхронизированная память с произвольным порядком выборки и удвоенной передачей данных. Появился этот тип памяти где-то в 1998 году и был сразу взят на вооружение производителями видеокарт. Затем DDR широко распространилась и на материнские платы. На сегодняшний день, этот тип памяти, пожалуй, наиболее применяемый в персональных компьютерах. Ведь DDR сочетает в себе приемлемую скорость и при этом относительную дешевизну.

Рис.2.1.8.1 Стандартный модуль DDR SDRAM

Принцип работы DDR SDRAM очень схож с обычной SDRAM (отсюда и второе название DDR SDRAM – SDRAM 2). Память разбита на страницы, каждая страница разбита на банки. Работа памяти синхронизирована с тактовым генератором системной платы. Основное отличие заключается в том, что за один цикл происходит два обращения к данным: по фронту и срезу импульса тактового сигнала системной шины. Говоря простым языком, чтение/запись происходит два раза за один такт. Кроме того, частота работы повышается за счет применения интерфейсных логических схем с еще более пониженным уровнем питания. Если для SDRAM обычно используются схемотехнические решения на базе LVTTL (Low Volt Transistor-to-Transistor Logic) с напряжением питания 3,3 В, то в DDR SDRAM - на базе SSTL (Stub Series Terminated Logic) с напряжением 2,5 В (а в перспективе и SSTL-2 с напряжением 1,25 В).

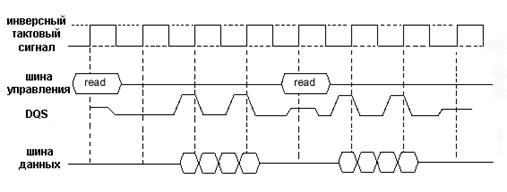

DDR SDRAM управляется инверсными тактовыми сигналами. Управляющие и адресные сигналы регистрируются по положительному фронту тактового сигнала, точнее при переходе сигнала с низкого уровня напряжения на более высокий, а вот данные передаются по обоим фронтам сигнала. Такая схема работы требует более четкой синхронизации. Для этого введен дополнительный стробовый сигнал DQS. Говоря просто, этот сигнал необходим для согласования передачи данных при чтении из памяти и контроллером при записи в память. До кучи, следует отметить, что при передаче данных по фронту и срезу сигнала синхронизации критичным будет лишь время задержки распространения сигнала. Вот и пришлось использовать этот строб-сигнал.

Рис.2.1.5.2 Временная диаграмма DDR SDRAM

При тактовой частоте системной шины 100 МГц скорость передачи данных будет равна 1600 Мбайт/сек, а при 133 МГц – 2100 Мбайт/сек. Отсюда следуют названия памяти DDR – РС1600 и РС2100. Максимальная же пропускная способность при результирующей частоте в 400 Мгц может достигать 3,2 Гбайт/сек.

Следует упомянуть тот факт, что микросхемы SDRAM и DDR физически не совместимы: в первом случае микросхемы имеют 168 контактов, во втором – 184. Отсюда несколько разное расположение ключа. Кроме этого, не все чипсеты поддерживают тот или иной тип памяти.

В ближайшее время на рынке должна появится DDR 2. В этом типе памяти данные будут передаваться не 2 раза, а 4, что позволит повысить максимальную пропускную способность до 6,4 Гбайт/сек, и это позволит продлить жизнь DDR в мире инфотехнологий.

2.1.9 RDRAM (RambusDRAM)

Direct Rambus DRAM - это высокоскоростная динамическая память с произвольным доступом, разработанная Rambus, Inc. Она обеспечивает высокую пропускную способность по сравнению с большинством других DRAM. Direct Rambus DRAMs представляет интегрированную на системном уровне технологию.

Технология Direct Rambus представляет собой третий этап развития памяти RDRAM. Впервые память RDRAM появилась в 1995 г., работала на частоте 150 МГц и обеспечивала пропускную способность 600 Мбайт/с. Она использовалась в станциях SGI Indigo2 IMPACTtm, в приставках Nintendo64, а также в качестве видеопамяти. Следующее поколение RDRAM появилось в 1997 г. под названием Concurrent RDRAM. Новые модули были полностью совместимы с первыми. Но за год до этого события в жизни компании произошло не менее значимое событие. В декабре 1996 г. Rambus, Inc. и Intel Corporation объявили о совместном развитии памяти RDRAM и продвижении ее на рынок персональных компьютеров. Вопреки распространенному мнению, ее архитектура довольно прозаична и не блещет новизной. Основных отличий от памяти предыдущих поколений всего три:

а) увеличение тактовой частоты за счет сокращения разрядности шины, б) одновременная передача номеров строки и столба ячейки, в) увеличение количества банков для усиления параллелизма.

Повышение тактовой частоты вызывает резкое усиление всевозможных помех и в первую очередь электромагнитной интерференции, интенсивность которой в общем случае пропорциональна квадрату частоты, а на частотах свыше 350 мегагерц вообще приближается к кубической. Это обстоятельство налагает чрезвычайно жесткие ограничения на топологию и качество изготовления печатных плат модулей микросхемы, что значительно усложняет технологию производства и себестоимость памяти. С другой стороны, уровень помех можно значительно понизить, если сократить количество проводников, т.е. уменьшить разрядность микросхемы. Именно по такому пути компания Rambus и пошла, компенсировав увеличение частоты до 400 MHz (с учетом технологии DDR эффективная частота составляет 800 MHz) уменьшением разрядности шины данных до 16 бит (плюс два бита на ECC).

Рис.2.1.9.1 Модули памяти RDRAM

Второе (по списку) преимущество RDRAM - одновременная передача номеров строки и столбца ячейки при ближайшем рассмотрении оказывается вовсе не преимуществом, конструктивной особенностью. Это не уменьшает латентности доступа к произвольной ячейке (т.е. интервалом времени между подачей адреса и получения данных), т.к. она, латентность, в большей степени определяется скоростью ядра, а RDRAM функционирует на старом ядре.

Большое количество банков позволяет (теоретически) достичь идеальной конвейеризации запросов к памяти, несмотря на то, что данные поступают на шину лишь спустя 40 нс. после подачи запроса (что соответствует 320 тактам в 800 MHz системе), сам поток данных непрерывен.

Емкость серийно выпускаемых модулей Rambus DRAM составляет 64, 128 и 256 Мб, в дальнейшем ожидаются изделия по 1 Гб. Так как использование 9-го бита на каждый байт данных оставлено на усмотрение производителя, одни фирмы вводят функцию ЕСС, другие увеличивают емкость чипов. В последнем случае получаются модули емкостью 72, 144 или 288 Мб.