Микроконтроллеры семейства Zilog Z86Рефераты >> Программирование и компьютеры >> Микроконтроллеры семейства Zilog Z86

Рис. 1.24. Структурная схема организации прерываний

|

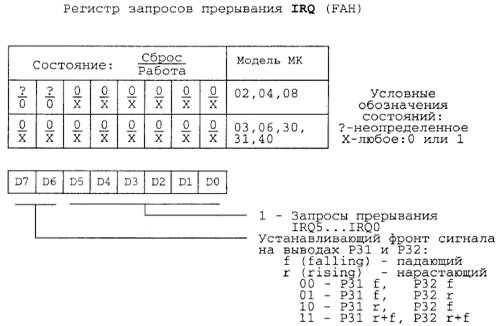

Рис. 1.25. Регистр запросов прерывания IRQ

|

Рис. 1.26. Регистр маски прерываний IMR

Регистр приоритета прерываний IPR (рис.1.27) позволяет устанавливать любое соотношение приоритетов как между группами прерываний А, В, С, так и между отдельными запросами прерываний внутри группы. В каждую группу включено по два запроса.

|

Рис. 1.27. Регистр приоритетов прерываний IMR

В случае векторного процесса каждый уровень прерывания имеет собственный вектор —адрес подпрограммы обслуживания этого уровня прерывания. Векторы прерываний размещены в начальной зоне ПЗУ (см. рис. 1.3). Инициализация процесса векторного прерывания происходит, если прерывания глобально разрешены и есть хотя бы один незамаскированный запрос прерывания. Если таких запросов несколько, то выбирается вектор прерывания с наивысшим приоритетом. Далее реализуется следующая последовательность действий:

— загружается в стек младший байт PC;

— загружается в стек старший байт PC;

—загружается в стек регистр флагов FLAGS;

— читается старший байт вектора;

— читается младший байт вектора;

—вектор загружается в PC.

Эта последовательность занимает 24 такта синхронизации TpC. Наихудшее время реакции на прерывание можно вычислить, прибавив к этому времени 2TpC для синхронизации внешнего запроса прерывания и время выполнения самой длинной команды в прерываемой программе.

1.3. Система команд микроконтроллеров Z8

Математические возможности МК характеризуются системой команд. В МК использован двухадресный принцип построения команд, что позволяет сократить количество требуемых пересылок операндов. Первый операнд после выполнения команды становится результатом и называется операндом-получателем ( Destination Operand ), а второй —сохраняет свое значение и называется операндом-источником ( Source Operand ). Первый в описании системы команд обозначен аббревиатурой dst, а второй —src.

Код любой команды МК содержит код операции (КОП), определяющий операцию команды, и до двух адресных полей. Способы трактовки кодов в адресном поле называются способами адресации операндов.Прежде чем рассматривать набор команд, необходимо более подробно рассмотреть используемые способы адресации операндов.

1.3.1. Способы адресации операндов

В МК Z8 использовано шесть основных способов адресации операндов :

— регистровая ( Register );

— косвенная регистровая ( Indirect Register );

— индексная ( Indexed );

— прямая ( Direct );

— относительная ( Relative );

— непосредственная ( Immediate ).

Кроме того, регистровая и косвенная регистровая адресации имеют ряд модификаций: они могут использовать сокращенный 4-битный адрес рабочего регистра, полный 8-битный адрес регистра, сокращенный 4-битный адрес рабочей пары регистров, полный 8-битный адрес регистровой пары. При адресации пар регистров используется четное выравнивание, т.е. допустимые адреса —четные числа. Шестнадцатибитные операнды занимают в регистровом файле пару регистров, причем по четному адресу размещается старший байт.

Все способы адресации операндов в системе команд МК Z8 приведены в табл.1.7. В таблице указаны условные обозначения способов адресации, используемые в дальнейшем в таблице команд, наименование способа адресации, обозначение операнда на языке ассемблера, диапазон значений адреса и номер рисунка, на котором дана графическая интерпретация способа адресации.

Следует отметить, что адреса типа R, RR, IR, IRR предполагают использование как полного 8-битного адреса регистра, так и сокращенного 4-битного. В последнем случае адрес размещается в младшей тетраде адресного байта, а в старшей тетраде указывается код 1110B (EH) :

|

E |

Dst/src |

Поэтому обращение к регистрам рабочей группы E СРФ возможно только с помощью рабочей регистровой адресации (см. п.п.1.2.2.1).

Таблица 1.7. Способы адресации операндов

|

Способ |

Наименование |

Операнд |

Диапазон |

Рис. |

|

r |

Рабочая регистровая(РР) |

Rn |

n=0, .,15 |

1.35 |

|

R |

Регистровая или РР |

Reg Rn |

00H —FFH n=0, .,15 |

1.36 1.35 |

|

RR |

Регистровая пара или PP пара (четное выравнивание) |

Reg RRp |

00H —FEH p=0, .,14 |

1.38 1.37 |

|

Ir |

Косвенная РР |

@Rn |

n=0, .,15 |

1.39 |

|

IR |

Косвенная регистровая или косвенная РР |

@Reg @Rn |

00H —FFH n=0, .,15 |

1.40 1.39 |

|

Irr |

Косвенная через РР пару |

@RRp |

p=0, .,14 |

1.41 |

|

IRR |

Косвенная через регистровую пару или РР пару |

@Reg @RRp |

00H —FEH p=0, .,14 |

1.42 1.41 |

|

X |

Индексная |

Reg(Rn) |

00H —FFH |

1.43 |

|

DA |

Прямая |

Addrs |

0H —FFFFH |

1.44 |

|

RA |

Относительная |

Addr |

-128- +127 |

1.45 |

|

IM |

Непосредственная |

#Data |

00H —FFH |

1.46 |