Микроконтроллеры семейства Zilog Z86Рефераты >> Программирование и компьютеры >> Микроконтроллеры семейства Zilog Z86

В моделях 03, 06, 30, 31 и 40 управление схемой синхронизации осуществляется путем записи управляющей информации в регистры PCON и SMR в процессе выполнения прикладной программы МК (см. нижнюю часть рис 1.4). Бит D7 регистра PCON управляет режимом задающего генератора, а биты D1 и D0 регистра SMR -делителями на 2 и на 16 соответственно. Логика управления показана на схеме.

_ * В модели 03 делитель на 16 отсутствует, а бит D0 зарезервирован и должен быть равен 0. В моделях 02,04,08 делитель на 16 отсутствует.

|

Для устойчивого самовозбуждения генератора необходимо соблюдение условий баланса амплитуд и баланса фаз на частоте генерации. Условие баланса амплитуд заключается в равенстве 1 произведения коэффициента усиления усилителя на коэффициент передачи цепи обратной связи. Условие баланса фаз требует, чтобы суммарный сдвиг фаз в схеме был равен 0 (360о). Поскольку инвертирующий усилитель дает сдвиг фазы 180о, то цепь обратной связи должна обеспечивать фазовый сдвиг также на 180о.

|

1.2.4. Сброс и сторожевой таймер

Функция сброса (Reset) необходима для инициализации важнейших элементов МК: схемы управления и синхронизации, программного счетчика (он устанавливается в состояние 000СН), управляющих регистров и портов (для определения их состояния после сброса для разных моделей МК, см. приложение 1).

Функция сброса активируется в следующих случаях: - при подаче низкого уровня на вход /RESET (только для модели 40); - при включении питания VСС; - при переполнении сторожевого таймера WDT; - при восстановлении из режима STOP.

В последнем случае (так называемый "теплый" старт) и в случае переполнения сторожевого таймера в режиме STOP порты и управляющие регистры не реинициализируются.

Функция сброса используется также для защиты памяти МК от падения напряжения питания. Это обеспечивается включением функции сброса при падении питающего напряжения VСС ниже порога защиты VLV (Low Voltage) -2-.6 В. Если уровень напряжения не снизится ниже уровня работоспособности КМОП-логики VCMOS (1.2 В), то возможно сохранение содержимого памяти МК и продолжение нормальной работы после восстановления VСС и автосброса. Это позволяет защитить МК от кратковременных "провалов" питающего напряжения.

|

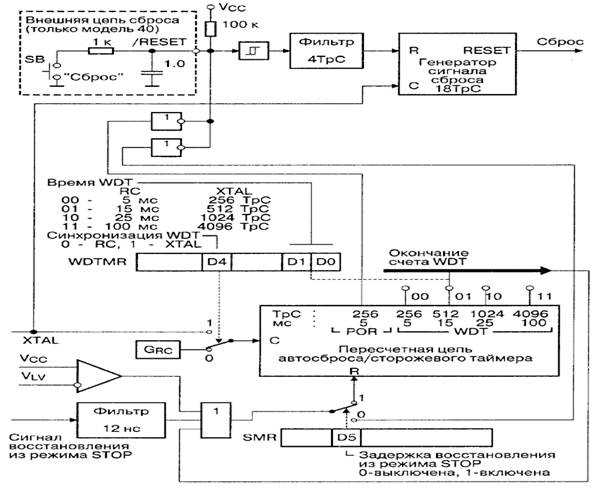

Обобщенная структурная схема сброса и сторожевого таймера показана на рис. 1.7. Рис. 1.7. Схема сброса/сторожевого таймера

Схема содержит генератор сигнала внутреннего сброса, синхронизируемого импульсами основного генератора XTAL. Этот генератор обеспечивает минимальную длительность сигнала сброса 18 периодов TpC частоты XTAL. Запуск генератора осуществляется через фильтр длительности в 4 TpC. Иначе говоря, если длительность запускающего сигнала будет меньше 4 TpC, то сброса не произойдет. Если запускающий сигнал длиннее 18 TpC, то сброс будет удерживаться на время этого сигнала плюс 18 TpC.

Объединение сигналов запуска сброса осуществляется по схеме "монтажное ИЛИ", поэтому к внешнему выводу МК /RESET (только для модели 40) можно подключать схемы с выходными каскадами с открытым стоком. Для сброса МК с помощью кнопки SB "Сброс" следует применять внешнюю RC-цепь, показанную на том же рисунке. Для возможности использования RC-цепи вход запуска дополнен триггером Шмитта.

Таймер автосброса POR (Power-On Reset) и сторожевой таймер WDT (Watch-Dog Timer) выполнены в виде пересчетной цепи, которая, в общем случае, синхронизируется от дополнительного RC-генератора GRC или от основного генератора XTAL. Таймер POR имеет для всех моделей постоянное время, а таймер WDT -программируемое (за исключением моделей 02, 03, 04 и 08).

Запуск таймера автосброса POR осуществляется в следующих случаях: - если уровень VСС поднимается выше уровня VLV; - если становится активным сигнал восстановления из режима STOP; - если имеет место окончание счета сторожевого таймера WDT.

В первом случае сигнал запуска вырабатывается специальным компаратором А. Во втором случае паразитные всплески сигнала источника подавляются фильтром 12 нс.

Во всех этих случаях происходит запуск таймера автосброса POR, время задержки которого гарантирует окончание переходных процессов в цепи питания VСС и выход на нормальный режим основного генератора синхронизации XTAL, после чего корректно выполняется внутренний сброс МК.

При восстановлении из режима STOP в случае применения LCили RC-времязадающих цепей основного генератора (см. п.1.2.3) нет необходимости выдерживать задержку автосброса, т.к. эти конфигурации генератора имеют малое время установления. Для сокращения задержки восстановления из режима STOP в этом случае сигнал от источника может быть подан непосредственно на вход запуска генератора сигнала сброса. При этом необходимо, чтобы сигнал от источника восстановления имел длительность не менее 4 TpC.

В МК, имеющих расширенную группу регистров F (модели 03, 06, 30, 31, 40), управление схемой сброса / сторожевого таймера осуществляется с помощью регистров режима сторожевого таймера WDTMR (Watch-Dog Timer Mode Register) и режима восстановления из режима STOP-SMR (STOP-Mode Recovery Register). Логика управления понятна из рисунка. Следует отметить, что поскольку генератор основной синхронизации выключается в режиме STOP, прежде чем перейти в этот режим необходимо, чтобы бит D4 WDTMR был установлен в состояние 0. Необходимо помнить, что регистр WDTMR доступен для записи только в течение первых 64 тактов (128 TpC) процессора после сброса, вызванного любым источником. Назначение разрядов регистра WDTMR полностью показано на рис. 1.8.

|